Digitimes 無人載具技術關鍵路徑研討會活動

瞭解更多關於無人機高密度電源轉換的詳情

利用多相降壓穩壓器的傳統方法正受到極大挑戰,因此需要採取一種新方法來跟上步伐。

作者:Paul Yeaman,應用工程高級總監

高性能處理器在壓擺率急劇上升的情况下,需要更高的穩態和峰值電流,而在高速 I/O 的數量不斷增加時,工作電壓將會降低。這一趨勢正在加劇,不斷為電源系統設計人員帶來確保在供電網絡(PDN)中以低損耗形式為處理器內核提供足够電源的挑戰。

使用多相降壓穩壓器的常規方法挑戰性越來越大,跟上時代發展的步伐需要製定一種全新的方案。

Vicor 分比式電源架構(FPA™) 與通用多相位方法不同,它能够以獨特的方式解决全新處理器科技的 VR 開發所面臨的各項挑戰。此外,FPA 還支持橫向供電(LPD)和垂直供電(VPD)PCB 部署選項。VPD 解決方案可將損耗銳降 95%,並可通過釋放 100% 的處理器周邊空間來消除瓶頸。

先進的 GPU 和專用人工智慧處理器正在推動人工智慧(AI)的快速發展,這些處理器採用先進的 7 納米、5 納米矽工藝節點,並迅速向 3 納米靠近。這些工藝節點的額定覈心工作電壓現時在 0.75V 到 0.85V 之間。為了達到 AI 要求的效能工作負載,額定流耗增大了,電流超過了600A 的穩態電流和 1000A 的峰值電流。這一趨勢比兩年前增長了兩倍,而且這一增長速度還在繼續。

電壓的降低和電流的新增帶來了兩個問題。首先,電流的新增加劇了主機板 PCB 的銅損耗,因為連接 VR 和處理器的銅箔層和通孔電阻有限。新增處理器電流將以電流的平方新增損耗,而降低效率將為處理器熱管理系統帶來大量額外的熱量。其次,PDN 上的壓降與電流的新增成正比。核心電壓下降時,該壓降的效應將對處理器效能產生巨大影響。

例如,100μΩ 線迹的 400W 核心負載會在 1V 線路上產生 4% 的下沖,而該核心負載則會在 0.75V 線路上產生 7% 的下沖,幾乎新增了 2 倍。供電網絡的物理限制使得降低這類電阻的選項非常有限。為主機板添加銅箔層或新增銅箔厚度,將降低電阻,但在 0.75V 電壓下會實現相同的4% 的壓降,線迹電阻不得不銳減近一半。由於成本或物理限制的原因,通常無法將銅箔數量新增一倍,以承載大電流。

簡而言之,更好的解決方案是將 VR 佈置在離處理器更近的地方。

雖然聽起來很簡單,但實施起來很複雜。首先,具有信號完整性挑戰。將硬切換多相 VR 靠近處理器,會帶來 VR 所具有的固有雜訊。所需分散相數進一步新增了問題的複雜性。

第二個挑戰是 VR 的封裝。典型的處理器封裝尺寸為 60 x 60 毫米。雖然這看起來很大,但需要注意的是,該區域的大部分空間都是 I/O 專用的。所有熱量都是在內核中產生的,所有的大電流都必須為其找一個路徑。

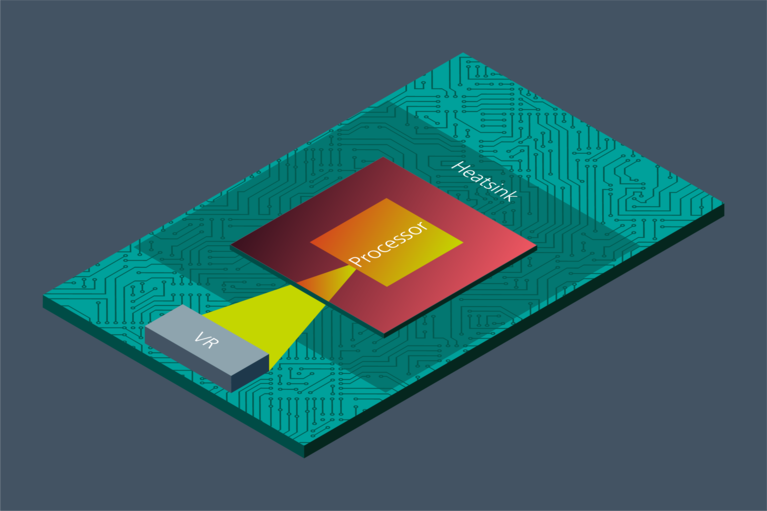

圖 1: 典型的處理器封裝尺寸均為 60 x 60 毫米,以紅色顯示。所有電流均由中間的內核消耗。通往內核的路徑中的 PCB 電阻損耗和寄生電容/電感是被稱為”最後一英寸“的難點,也是確保處理器效能最大化的限制因素。

這意味著,即使 VR 佈置在封裝邊緣的附近,仍有一個大電流必須流向內核的有效距離。在典型 VR 方案中,電流越大,相位就越多。由於大多數多相 VR 為分立式器件,囙此電感和開關級必須單獨佈置,在大多數情况下,還必須單獨散熱。囙此,相位越多,VR 就越大,其可新增靠近處理器佈置的挑戰性。

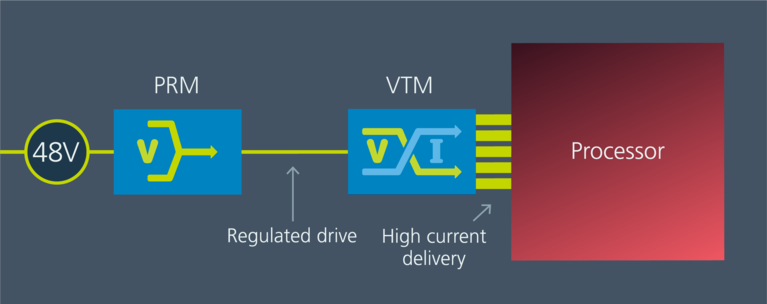

分比式電源架構(FPA™) 基於將電源轉換器分為兩大主要功能、分別對每個功能進行優化,然後按一個系統實施這些功能的基本原理。這兩個功能是穩壓和電流倍增。

穩壓器的效率與所執行的工作成反比:工作越多,效率越低。穩壓器輸入輸出電壓越接近,所做的工作就越少、效率就越高。FPA 可憑藉其在系統中的位置,最大限度降低穩壓器輸入至輸出之間的壓差。PRM™ 穩壓器採用零電壓開關(ZVS)升降壓拓撲實施,在輸入輸出壓差很小的情况下,具有高效率。零電壓開關可顯著降低開關損耗,囙此不僅可實現高頻率工作,而且還可大幅縮小轉換器尺寸。PRM 通常將輸入電壓穩定在 40 至 60V 之間,輸出電壓穩定在 30 至 50V 之間。

PRM 之後是執行降壓與增流功能的第二階段。這是在一個名為 VTM™ 電流倍增器的器件中使用正弦振幅轉換器拓撲實施的。VTM 的性能可按理想變壓器實現,其中輸入輸出電壓之間有固定比例的關係,器件阻抗在 1MHz 以上保持為低(幾百微歐)。

VTM 中沒有能量存儲,因此,如果散熱良好,它可提供大量的電源。這可將 VTM 的電源容量與處理器的散熱功能相匹配。PRM 和 VTM 都是FPA 的構建塊。

圖 2: PRM 和 VTM 都是 FPA 的構建塊。根據系統輸入電壓範圍和電源要求選擇 PRM 並根據輸出電壓範圍和電流要求選擇 VTM 。PRM 可安裝在系統中任何便捷的地方,而 VTM 則應該安裝在儘量靠近處理器內核的位置。

一個專門穩壓,而另一個專門變壓。

雖然用於實施高性能穩壓器的拓撲和架構很重要,但封裝技術也很重要。Vicor 的 SM ChiP™ 封裝將無源、磁性、FET 和控制等所有組件都集成在一個統一器件中。此外,該封裝經過精心設計,能够以更低的熱阻抗,實現更高效的電流選取,從而可增强散熱。此外,許多 SM-ChiP 還包括器件重要表面的接地金屬遮罩。這不僅有助於散熱,而且還可當地語系化高頻率寄生電流,以防止將其傳播到器件外。

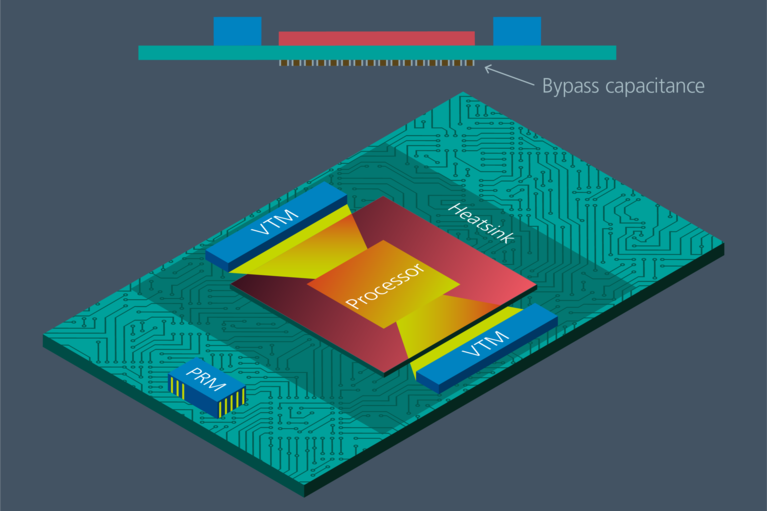

圖 3: 在 AI 加速卡上支持主線路電源的典型 PRM/VTM 分比式電源架構解決方案。將 VTM 佈置在插座兩對面,不僅可將流經供電網絡進入處理器的電流分成兩半,而且還可將損耗銳降 50%。

為了給廣泛的應用實施方案提供高度的靈活性,Vicor 開發了 PRM 和 VTM,其所提供的功率級細微性可為降低 PDN 損耗實現高度的靈活性。例如,將單個較大電流的 VTM 按兩個較小的較小電流 VTM 實施,允許將其佈置在處理器插座的兩對面。這可將供電網絡的損耗銳降 50%,從而可將電流分成兩半,並可為覈心區域新增一條獨立的路徑。

為 2. 8 毫米時,VTM 比大量機械處理器支持元件薄,如封裝插座、加强筋以及散熱器附件硬體等。將 VTM 佈置在這些元件下,可使其與處理器熱管理系統耦合,無需專用 VTM 散熱器,同時可通過將電流倍增器佈置在更靠近內核的位置,降低供電網絡的損耗。

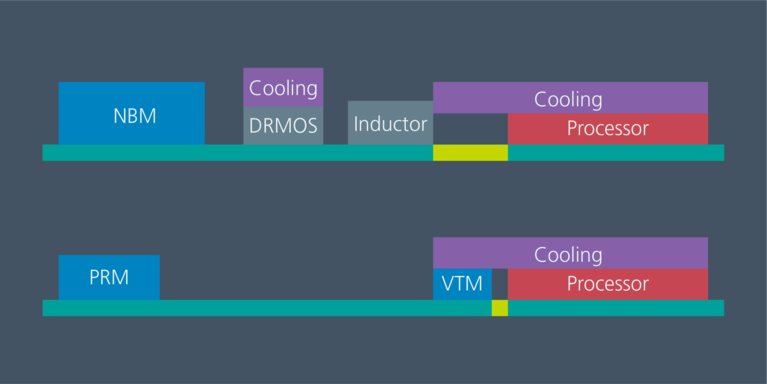

圖 4: 在典型的多相位 VR 中,相位感應器的高度通常會限制相位感應器與處理器的距離,而且 DRMOS 級需要單獨的散熱。纖薄的 VTM 有助於將其移到處理器散熱片及相關硬體之下,而 PRM 則可在不影響效能的情况下,佈置得更遠一些。

這些都是橫向供電(LPD)的示例。在 LPD 中,電流倍增器位於主機板的處理器側,電流會從 VR 橫向流入處理器。因此,這會產生固有的損耗,無論電流倍增器與處理器內核距離有多近,都是不可避免的。

垂直供電(VPD)是應對這種固有損耗的解決方案。在 VPD 中,電流倍增器位於處理器的背面,也就是它的正下方。

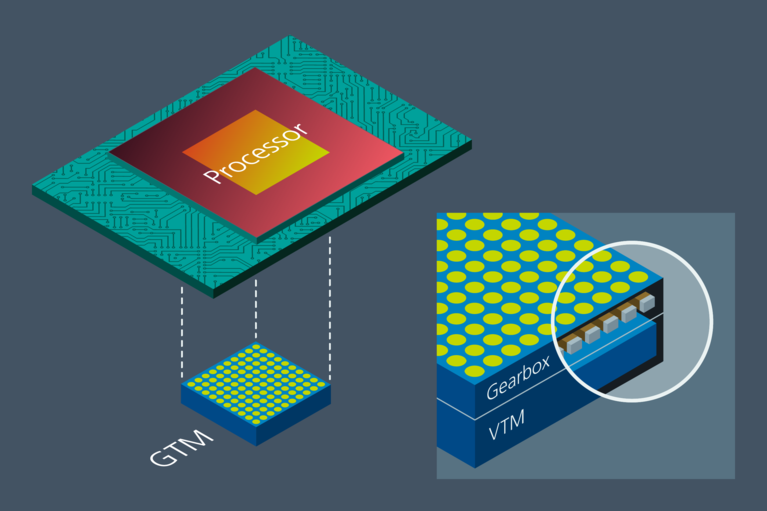

圖 5: 垂直供電(VPD),將 類似 GTM 齒輪傳動電流倍增器佈置在處理器下方,可最大限度提高供電性能。此外,VPD解決方案還可為更高的 I/O 路線、板載記憶體或更緊密的處理器集羣等多種選項減輕處理器頂部週邊的壓力。

縮短電流通過主機板的距離,可顯著降低 PDN 損耗。VPD 需要兩個關鍵特性來實現該功能。

首先,處理器正下方的區域通常提供有高頻率電容器,這是為來自系統其餘部分的極高頻率電流(超過 10MHz)去耦所必需的。其次,為了最大限度提高效率,輸出 VPD 解決方案的電流的物理位置和模式必須準確鏡像處理器內核電源輸入的位置和模式。這有助於大電流實現真正的“垂直”輪廓。

為實現這些特性,Vicor VPD 解決方案還包含使用齒輪箱實現的 VTM 電流倍增器,因此支持 GTM™ 齒輪傳動電流倍增器。齒輪箱有兩種功能:它包含高頻率去耦電容,可將來自 VTM 的電流重新分配給鏡像其上處理器的模式。GTM 中 VTM 陣列的大小主要由處理器輸出電流要求來决定,而齒輪箱 BGA 模式則主要由處理器來决定。因此,GTM 是標準(VTM)和客戶(齒輪箱)解決方案的完美組合。

採用 SM-ChiP 封裝來實施分比式電源架構 LPD 和 VPD 解決方案,能够顯著降低低電壓、大電流處理器的供電網絡損耗。隨著處理器電流要求不斷攀升至 1000A 甚至更高,Vicor 分比式電源架構不僅能够提供更低的核心電壓和更大的覈心電流,同時還能降低供電網絡損耗並提高系統效率。

本篇文章由 Bodo's Power Systems 首發。

Paul Yeaman 與行業中的科技領導者廣泛合作,開發和實施了系統中領先的電源解決方案,這些解決方案滿足行業中嚴苛的電源需求。由於經常接觸新技術帶來的電源挑戰,Paul 瞭解電源行業的廣泛趨勢,並致力於確保創新者能够綜合電源解決方案以滿足這些需求。Paul 在電力電子行業的設計和應用工程領域有 20 多年的經驗。

Paul Yeaman, 應用工程高級總監